# Recycling Of Electronic Components For The Manufacture Of Photovoltaic Cells

Tiganà MANDIMBY, Mahery SOMBINIAINA, Eulalie RAFANJANIRINA, Thierry RANDRIANARINOSY, Zely RANDRIAMANATANY.

University of Antananarivo, Madagascar

Corresponding author: J. J Zoé Tiganà MANDIMBY; zoetigana@gmail.com

Abstract – In a context where recycling of electronic components is becoming increasingly important for sustainable development, this work is part of an innovative approach aimed at valorizing existing materials. The objective is to design a photovoltaic cell from recycled transistors. A bibliographic study on photovoltaic generators has provided a better understanding of the operation of a photovoltaic cell for the production of electricity.

To achieve this objective, a study and modeling of Si/SiGe heterojunction bipolar transistors (HBTs) from the BiCMOS sector were carried out. After recalling the operating principle of bipolar transistors as well as their main electrical and physical characteristics, the properties of the SiGe alloy were analyzed. This analysis highlighted the impact of germanium on the performance of HBTs.

The experimental results obtained demonstrated the efficiency of the photovoltaic generator made from 2N3055 transistors Keywords: Photovoltaic, BiCMOS technology, heterojunction bipolar transistor TBH, SiGe alloy

Keywords - Photovoltaic, BiCMOS technology, TBH heterojunction bipolar transistor, SiGe alloy.

# I. INTRODUCTION

The growth of the semiconductor industry currently relies on its ability to miniaturize the components it produces. The primary objective is to achieve the best performance while minimizing costs. Smaller circuits reduce the overall surface area of electronic chips, allowing more components to be integrated onto the same wafer and lowering manufacturing costs.

The increase in integration density and the improvement of performance are made possible by the reduction in transistor cell sizes. Transistors, which play a critical role in integrated circuits, are present in large numbers. A key characteristic that differentiates one generation of transistors from another is the length of the gate (LG).

At present, the smallest gate length produced is 37 nm, and further size reductions are essential for driving technological innovation. The International Technology Roadmap for Semiconductors (ITRS), whose forecasts are established by leading semiconductor industries, predicted a gate length of 9 nm by 2016 [1].

However, such dimensions generate technological problems that are much more complex and especially different from those encountered in current transistors. In addition to the need to optimize manufacturing processes, it is essential to know the physical limits of Complementary Metal-Oxide-Semiconductor (CMOS) technology beyond which a technologically perfect transistor will have more tolerable electrical properties. Although the answer is not yet obvious, it appears clear that new architectures must replace, in the more or less long term, conventional transistors. It has already been decided, for example, to no longer make a type of transistor valid for all applications, but a particular architecture according to the applications including those of "high performance" (microprocessors) or those of "low consumption" (portable phones) ). The development of nanometric transistors meets experimental problems and theoretical challenges. It is crucial to overcome them so that the momentum towards

miniaturization is not stopped or abandoned. The sustained diminution of these dimensions accelerates the synergy of microelectronics and quantum mechanics as well as the laws that govern the transport of electrons. The simulation of transistors thus requires new theories and modeling techniques such as artificial modeling improving the physical comprehensibility of positives. nanometer-sized. Despite this advance in miniaturization, the manufacturing of electronic components is still booming for their various applications. The recycling of waste electronic materials such as diodes and transistors are very interesting given their actual number. Among them, there is the manufacture of photovoltaic cells to create a new source of electric generator or the production of electricity that can satisfy the domestic and industrial needs of man. Indeed, photovoltaics is part of the alternative solutions to various problems that must be faced, such as the preservation of the environment due to the emission of greenhouse gases (GHG), deforestation. Solar panels can be recycled. The recovered materials can be reused for the manufacture of new panels. We study the theoretical system of the photovoltaic system and the architectures of the transistor to have the ease of explanation of the photovoltaic phenomenon applied to the transistor which creates electric current from the photon like the operation of the panel system. The objective of this article is to characterize the SiGe heterojunction bipolar transistor in order, first, to demonstrate its potential to manufacture photovoltaic cells from waste electronic components such as diodes and transistors, then to obtain a small generator low voltage or low power direct current that can light a Véies lamp or a 5V phone charger.

#### II. METHODOLOGY

# 2.1. Introduction

Photovoltaic materials, as intelligent composites utilizing photovoltaic technology, are reviewed in this section with their associated terms and applications. Each application is analyzed to identify the scientific challenges encountered during integration and operation.

To ensure durability over time and minimize breakdowns and energy losses, it is crucial to thoroughly study the connections and the physical and electrical behavior of these materials. This chapter addresses these issues, outlining the difficulties and presenting the solutions explored during the design and development of successive prototypes.

By the end of this chapter, the technological choices made and the potential advancements in electrical energy production are justified.

## 2.2. Conversion of Photons to Electrons

A photon with energy EEE can release an electron from the valence band, transferring its energy if EEE is equal to or greater than the energy gap EgE\_gEg. The freed electron participates in conduction, leaving behind an empty spot referred to as a "hole" in the valence band. Any excess photon energy not used in freeing the electron is converted into heat or kinetic energy.

The electron-hole pair created has a lifetime on the order of a picosecond before recombination occurs. To facilitate and control the dissociation of electrons, thus preventing recombination, an electric field is introduced through semiconductor doping. Doping involves adding impurities to the crystal structure of the material.

In silicon cells, this forms a PN junction, while in amorphous silicon cells, it may create a PIN or NIP junction. In such cases, layer III is undoped and facilitates the collection of charge carriers via the electric field.

- P-type doping is achieved by adding acceptor atoms with a valence lower than that of the semiconductor.

- N-type doping, on the other hand, is realized by replacing atoms in the semiconductor with donor atoms of higher valence. Electrons in the N region act as majority carriers, while holes are the minority carriers. Conversely, in the P region, holes are the majority carriers and electrons are the minority carriers.

For silicon semiconductors, doping of types P and N is achieved using elements from columns III (13) and V (15) of the Mendeleev Periodic Table, respectively.

Regions in the silicon cell are thus defined as follows:

- Base: P-type region.

- Space Charge Region (SCR): An insulating area with a strong electric field directed from the emitter to the base.

- Emitter: N-type region.

The space charge region forms a boundary between the emitter and base. It is established by majority carriers moving into regions where they are the minority, disrupting electrical neutrality. The fixed charges remaining create a positive charge on the N side and a negative charge on the P side.

This charge accumulation polarizes the direct junction, reducing the diffusion potential. This facilitates the flow of photocurrent through an external circuit, generating a photovoltage. When balance is disrupted by a photon with energy exceeding EgE\_gEg, an electron-hole pair forms within the P or N region. These pairs are then separated by the electric field in the depletion region.

The photocurrent produced is proportional to the light intensity and consists of:

- Generation Photocurrent: Caused by the electric field separating charge carriers in the depletion region.

- Diffusion Photocurrent: Generated by majority carriers entering the minority regions.

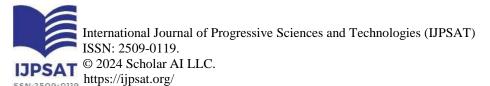

The operation of a photovoltaic cell can be summarized in Figure 1, which illustrates the process.

Figure 1: Operation of photovoltaic cells.

Its operation follows the following steps:

- Generation of electron- hole pairs;

- Diffusion of this pair towards the space charge zone;

- Electron- hole separation;

- Expulsion of the minority charge bearer towards the zone where he is majority (here the hole towards zone p)

- After passing through the charge, the electron and the hole recombine.

# 2.3. Transistor 2N3055

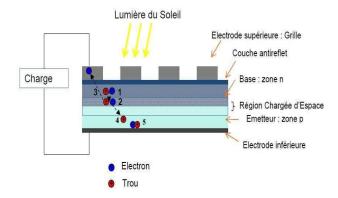

The 2N3055 transistor is organized around a SiGe structure according to the type arrangement shown in figure 26. Here, the insulator is an oxide (silica SiO 2); two îlots, of the opposite type to that of the substrate, the source and the drain, delimit the active region of the device that is located precisely under the grid electrode. The source is most often connected to the substrate.

The principle of the 2N3055 is very simple. For a P-type substrate for example, the application of a positive voltage on the grid relative to the substrate causes a negative space charge to appear on the surface of the semiconductor. As soon as the grid voltage exceeds a certain threshold  $V_T$ , an inversion layer is created and the channel N is thus formed, of the same type while the source and the drain are as many conductors that  $V_g$  are large and allow the passage of a current between the two islands of source and drain. Outside of the presence of this channel, that is to say for  $V_g < V_T$ , the source and drain islands form with the substrate of the PN junctions of which one is obligatorily found to be non-conducting whatever the polarity of the drain voltage; the conduction between drain and source is thus interrupted. For the moment, we assume that the source and the drain are in mass  $(V_sb=V_db=0)$ . In this case, three situations can be distinguished (in the canal region): accumulation, depletion and inversion as shown in figure 2.

Figure 2: Basic structure of a 2N3055 type transistor

# III. RESULTS

# 3.1. Analysis of the voltage created by a transistor

For negative grid voltages, the holes are attracted to the surface and a very fine layer of positive charges (the accumulation layer) is then formed with the increase of  $V_{gb}$ , the curvature of the bands becomes weaker, until a certain value où il n'y a plus de curbure des bands.

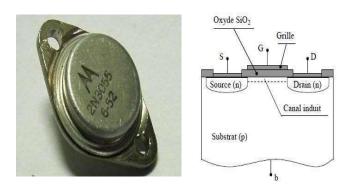

This particular value of grid tension is called the tension of flat bands. Beyond this point, the curvature of the bands is opposite to the accumulation cell, a negative charge is being formed. In fact, the positive charge on the grid repels the holes on the silicon surface and creates a negative charge (due to immobile acceptor ions), called a depletion charge. Figure 3 shows the charge obtained by a transistor.

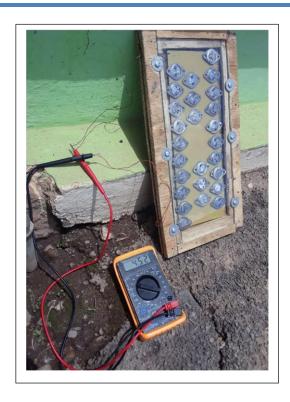

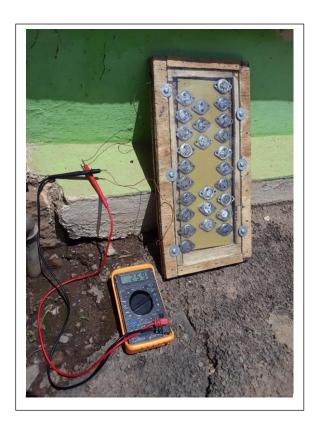

Figure 3: Measurement of the voltage generated by a transistor.

During the recycling process, we will transform the 2N3055 transistor into a voltage generator as shown in figure 3 which shows the tension measured at the terminals of its collector and base when it absorbs light photons and generates electron-hole pairs giving

Vol. 47 No. 1 October 2024, pp. 103-118

a continuous electrical voltage. The following table gives the measurement obtained by a generator of a photovoltaic cell that characterizes a current-voltage curve (I-V)

Table 1: Current-voltage values created by a transistor.

| U (V) | I (A)   | P(W)   |

|-------|---------|--------|

| 0.0   | 0.00370 | 0.0000 |

| 0.2   | 0.00370 | 0.0007 |

| 0.4   | 0.00369 | 0.0015 |

| 0.6   | 0.00369 | 0.0022 |

| 0.8   | 0.00369 | 0.0030 |

| 1.0   | 0.00368 | 0.0037 |

| 1,2   | 0.00368 | 0.0044 |

| 1.4   | 0.00368 | 0.0052 |

| 1.6   | 0.00367 | 0.0059 |

| 1.8   | 0.00367 | 0.0066 |

| 2.0   | 0.00366 | 0.0073 |

| 2,2   | 0.00365 | 0.0080 |

| 2,4   | 0.00362 | 0.0087 |

| 2.6   | 0.00354 | 0.0092 |

| 2.8   | 0.00340 | 0.0095 |

| 3.0   | 0.00320 | 0.0096 |

| 3.2   | 0.00290 | 0.0093 |

| 3,4   | 0.00260 | 0.0088 |

| 3.6   | 0.00220 | 0.0079 |

| 3.8   | 0.00170 | 0.0065 |

| 4.0   | 0.00100 | 0.0040 |

| 4.2   | 0.00000 | 0.0000 |

Vol. 47 No. 1 October 2024, pp. 103-118

Under un clairement given, any photovoltaic cell at the cell scale is characterized by a current-tension curve (I-V), figure 4 representing the set of electrical configurations that the cell can take. Two physical quantities define this curve:

- Or tension à vacuum  $V_{cc}$  representing the tension generated by a non-connected light cell;

- Son courant short-circuit  $I_{cc}$ , value of the current generated by an illuminated cell connected to itself;

Figure 4: Characteristics IV of a PV cell.

# 3.2. Study of voltage and current created by 5 transistors in parallel

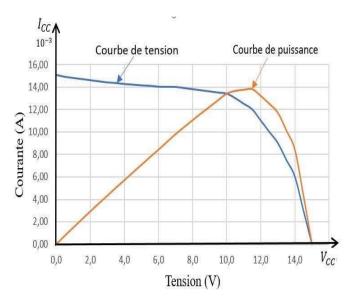

Figure 5 represents the result obtained by the association of 5 transistors in parallel, one of these transistors consists of producing a current of around 3mA, and 5 transistors generate a current of more than 15mA.

Figure 5: Current generated by 5 transistors connected in parallel.

It should be noted that each transistor has a voltage of 0.5V. However, after mounting these 5 transistors in parallel, the voltage obtained is reduced to 0.15V due to the state of the latter. Therefore, there is a reduction in tension in this montage made in parallel.

Figure 6 shows the tension obtained from the montage in parallel.

Figure 6: Voltage created by 5 transistors mounted in parallel

The measurement of voltage and current by this generator above gives the value in the following table.

Table 2: Current-voltage values created by 5 transistors in parallel.

| U (V) | I (A).10 | P (W).10 |

|-------|----------|----------|

| 0.0   | 15.07    | 0.00     |

| 0.5   | 14.90    | 0.75     |

| 1.0   | 14.80    | 1.48     |

| 1.5   | 14.70    | 2.21     |

| 2.0   | 14.60    | 2.92     |

| 2.5   | 14.50    | 3.63     |

| 3.0   | 14.40    | 4.32     |

| 3.5   | 14.35    | 5.02     |

| 4.0   | 14,26    | 5.70     |

| 4.5   | 14,20    | 6.39     |

| 5.0   | 14,14    | 7.07     |

SSN:2509-0119

Vol. 47 No. 1 October 2024, pp. 103-118

| 5.5  | 14,10 | 7.76  |

|------|-------|-------|

| 6.0  | 14.02 | 8.41  |

| 6.5  | 14.01 | 9,11  |

| 7.0  | 14.00 | 9.80  |

| 7.5  | 13.90 | 10.43 |

| 8.0  | 13.80 | 11.04 |

| 8.5  | 13.70 | 11.65 |

| 9.0  | 13.60 | 12,24 |

| 9.5  | 13.50 | 12.83 |

| 10.0 | 13.40 | 13.40 |

| 10.5 | 13.00 | 13.65 |

| 11.0 | 12.50 | 13.75 |

| 11.5 | 12.00 | 13.80 |

| 12.0 | 11.00 | 13,20 |

| 12.5 | 10.00 | 12.50 |

| 13.0 | 9.00  | 11.70 |

| 13.5 | 7.50  | 10,13 |

| 14.0 | 6.00  | 8.40  |

| 14.5 | 3.00  | 4.35  |

The following figure represents the characteristic curve of the current-tension (I-V) and the set of electrical configurations that can take the 5 cells of the transistor mounted in parallel.

0.00

0.00

15.0

Figure 7: Characteristic curve IV 5 cells in parallel.

#### 3.3. Representation of voltage and current created by 13 transistors in series .

Figure 8 shows a montage in parallel between two generators in series, the objective of this montage in parallel was to increase the intensity of the generator twice as a result.

Figure 8: Assembling the transistor in series.

Figure 9 represents the parallel assembly of two series of generators mounted in series.

SSN:2509-0119

Vol. 47 No. 1 October 2024, pp. 103-118

Figure 9: Mounting in parallel series of two generators mounted in series.

If one of these series-connected transistors failed, this would cause the current to be interrupted. We then had to add a diode by pass between the negative and positive terminals of each transistor. This diode prevents the return of the current, which can destroy the transistor. Also, we associated transistors in series to obtain a well determined voltage. During our experiment, 13 transistors mounted in series as shown in figure 10 gave a voltage of 4.5V.

SSN:2509-0119

Vol. 47 No. 1 October 2024, pp. 103-118

Figure 10: Voltage obtained by mounting the 13 transistors mounted in series .

In addition, after these experiments, we created a generator of voltage 4.5V and intensity 0.002A (or 2mA). The power obtained from the voltage and intensity of this generator was not sufficient to turn on a LED electroluminescent diode lamp

The power of this generator is  $P = U \times I = 4.5 \times 0.002 = 0.009W$

Figure 11 shows the intensity produced by the 13 transistors in series then mounted in parallel with the other 13 transistors in series.

Figure 11: Current produced by the 13 transistors in series made in parallel with 13 other transistors in series .

Table 3: Current-voltage values created by par 13 transistors in series made in parallel with 13 other transistors in series .

| U (V) | I (A). 10 | P (W).10 |

|-------|-----------|----------|

| 0,0   | 2,50      | 0,00     |

| 0,2   | 2,47      | 0,49     |

| 0,4   | 2,45      | 0,98     |

| 0,6   | 2,43      | 1,46     |

| 0,8   | 2,42      | 1,94     |

| 1,0   | 2,41      | 2,41     |

| 1,2   | 2,40      | 2,88     |

| 1,4   | 2,39      | 3,35     |

| 1,6   | 2,38      | 3,81     |

ssn:2509-0119 https://ijpsat.org/

Vol. 47 No. 1 October 2024, pp. 103-118

| 1,8 | 2,36 | 4,25 |

|-----|------|------|

| 2,0 | 2,34 | 4,68 |

| 2,2 | 2,32 | 5,10 |

| 2,4 | 2,30 | 5,52 |

| 2,6 | 2,25 | 5,85 |

| 2,8 | 2,18 | 6,10 |

| 3,0 | 2,10 | 6,30 |

| 3,2 | 2,00 | 6,40 |

| 3,4 | 1,90 | 6,46 |

| 3,6 | 1,70 | 6,12 |

| 3,8 | 1,50 | 5,70 |

| 4,0 | 1,20 | 4,80 |

| 4,2 | 0,80 | 3,36 |

| 4,5 | 0,00 | 0,00 |

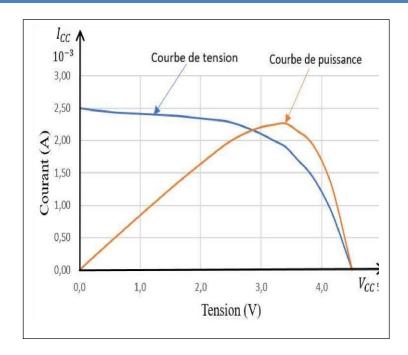

The current-voltage curve (I-V) representing the set of electrical configurations that can be obtained by 13 transistors in series made in parallel with 13 other transistors in series . So the two physical quantities define this curve (see figure 12)

Figure 12: Characteristic curve I-V 13 transistors in series made in parallel with 13 other transistors in series .

#### IV. DISCUSSION

In this article, we presented a study on a photovoltaic module made from recycled transistors. The measurements taken under real conditions allowed us to display the values recorded by the voltmeter. It was observed that a panel behaves as a voltage generator near the open-circuit voltage and as a current generator near the short-circuit current.

The electrical modeling of components is currently a highly sought-after research area worldwide. To keep up with this evolution, existing models must be improved and further developed, particularly in the context of electronic waste recycling.

Finally, the generation of current from recycled transistors requires a large number of transistors as the power output of the generator increases.

# V. CONCLUSION

The work presented in this article focuses on the modeling and optimization of a photovoltaic generator made from recycled components. The bibliographic study on photovoltaic generators allowed us to better understand the operation of photovoltaic cells and the application of photovoltaic modules in electricity production.

The development of a low thermal budget manufacturing process has significantly reduced the vertical dimensions of high-speed heterojunction bipolar transistors (HBTs). Numerous optimizations were made during the study. By limiting the diffusion of dopants in the base and emitter, solar panel modules and power transitions were achieved. We notably manufactured the first silicon technology transistor with transition power in a photovoltaic generator. Contrary to what might be thought, compatibility with a new generator manufacturing process is entirely possible. Indeed, the thermal budget of advanced generator technologies decreases with the generations of amorphous cells. The compatibility with the fabrication of an HBT, whose final activation annealing temperature is around the photon current, can be ensured from the node.

However, reducing the thermal budget presents several technological challenges. Insufficient activation of dopants leads to high resistance values, which penalize performance. Better control of the activation/diffusion tradeoff of dopants is therefore necessary to further improve the performance achieved in this study. The introduction of laser annealing (high energy/short times), which activates the dopants without causing diffusion, could be a solution.

Progress is also needed at the material level to reduce the resistivity of the layers that hinder the generator's performance. Finally, after significantly increasing the maximum power, advances in photolithography will help reduce the lateral dimensions of components, thus limiting parasitic elements. Recycling transistors for current generation is therefore an optimal solution to utilize electronic waste and facilitate the creation of solar panels.

# **REFERENCES**

SSN:2509-0119

| [01] | DJ Frank, RH Dennard, E. Nowak, Device scaling limits of Si MOSFETs and their application dependencies, Proc. IEEE , vol. 89, no. 3, pp. 259–288, 2001                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [02] | National Institute of Solar Energy (INES): <a href="http://www.institutsolaire.com">http://www.institutsolaire.com</a>                                                                                                                                                  |

| [03] | Revues: Solar systems, the observer of renewable energies: <a href="www.energies-renouvelables.org">www.energies-renouvelables.org</a>                                                                                                                                  |

| [04] | Pascal. Pernet "Development of 'nip'-type amorphous silicon solar cells on flexible substrates" Ecole Polytechnique Fédérale de Lausanne (EPFL), Thesis n°:2303, 2000                                                                                                   |

| [05] | National Institute of Solar Energy (INES): <a href="http://www.institutsolaire.com">http://www.institutsolaire.com</a>                                                                                                                                                  |

| [06] | ALLOUA F, ALBANEA (2012), "Study and implementation of a control strategy of a hybrid system (PV Diesel)", Final Thesis, Aboterrahmane Mira University, Bejaia.                                                                                                         |

| [07] | Matallah Sorya (2015), "Dimensioning and simulation of a PV system to power a habitat in Ouargla district", Final Study Memo, Kasdi University Merbah-                                                                                                                  |

|      | Ourgla.                                                                                                                                                                                                                                                                 |

| [08] | L. Militaru, A. Souifi, M. Mouis, A. Chantre, G Brémond, "Investigation of deep traps in silicongermanium epitaxial base bipolar transistors with a single polysilicon quasi self aligned architecture", Microelectronic Reliability, Vol. 41 No. 2, pp. 253 -263, 2001 |

| [09] | Boris GEYNET, "Development and study of bipolar transistors with Si/SiGe:C heterojunctions for millimetric BiCMOS technology" Thesis, University of Science and Technology of Lille, Page 16, 2010: <a href="http://doc.univ-lille1.fr">http://doc.univ-lille1.fr</a>   |

| [10] | Iyer, SS, Patton GL, Delage, SS, Tiwari, S., Stork, JMC, "Silicon-germanium base heterojunction bipolar transistors by molecular beam epitaxy". Technical Digest of IEDM 1987, Page(s): 874 - 876                                                                       |

| [11] | Ali Hajimiri and Thomas H. Lee, "The Design of Low Noise Oscillators", Kluwer Academic Publishers, ISBN :0-7923-8455-5, 1999.                                                                                                                                           |

| [12] | Shockley, W., "Circuit element utilizing semiconductive material" US patent 2,569,347, 25th Sept.1951                                                                                                                                                                   |

| [13] | Kroemer, H., "theory of wide-gap emitter for transistors" Proceeding of IRE, Vol.45,1957, Page(s): 1535 - 1537                                                                                                                                                          |

| [14] | E. Kasper, HJ Herzog, H.Kibbel, "A one-dimensional SiGesuperlattice frowned by UHV epitaxy", Journal of Applied Physics, Vol. 8, pp. 1541–1548, 1975.                                                                                                                   |

| [15] | SSIyer, GLPatton, SSDelage, S. Tiwari, JMCStork, "Silicon-germanium base heterojunction bipolar transistors by molecular beam epitaxy", Technical Digest of IEDM, pp. 874 -876, 1987.                                                                                   |

| [16] | E. Kasper, HJ Herzog, H.Kibbel, "A one-dimensional SiGesuperlattice frowned by UHV epitaxy", Journal of Applied Physics, Vol. 8, pp. 1541–1548, 1975.                                                                                                                   |

SSN:2509-0119

Vol. 47 No. 1 October 2024, pp. 103-118

- [17] DLHarame, , EFCrabbe, JD Cressler, JH Comfort, JYCSun, SR Stiffler, E.Kobeda, JN Burghartz, MM Gilbert, JC Malinowski, AJDally, S.Ratanaphanyarat, MJ Saccamango, W. Rausch, J. Cotte, C. Chu, JMC Stork, "A high performance epitaxial SiGe base ECL BiCMOS technology", Technical Digest of IEDM, p.19-22, 1992.

- [18] LD Lanzerotti, AS Amour, CW Liu, JCSturm, JKWatanabe, D. Theodore, "Si/Si1-x-yGexCy/Si heterojunction bipolar transistors", IEEE Electron Device Letters, Vol. 17, pp.334–337, July 1996.

- [19] SJ Jeng, B. Jagannathan, JS Rieh, J. Johnson, KT Schonenberg, D. Greenberg, A. Stricker, H. Chen, M. Khater, D. Ahlgren, G. Freeman, K. Stein, S. Subbanna, "A 210-GHz fTSiGe HBT with a non-self-aligned structure", in IEEE Electron Device Letters, Vol. .22, No.11, pp.542-544, Nov. 2001.

- JS Rieh, B. Jagannathan, H. Chen, KT Schonenberg, D. Angell, A. Chinthakindi, J. Florkey, F. Golan,

D. Greenberg, SJ Jeng, M. Khater, F. Pagette, C. Schnabel, P. Smith, A. Stricker, K. Vaed, R. Volant,

D. Ahlgren, G. Freeman, K Stein, S. Subbanna, "SiGe HBTs with cut-off frequency of 350 GHz", in

International Electron Devices Meeting Technical Digest, pp. 771774, 8-11 Dec. 2002.

- [21] N. Zerounian, F. Aniel, B. Barbalat, P. Chevallier, et A. Chantre, "500 GHz cutoff frequency SiGe HBTs", IEEE, Electronics Letters, Vol. 43 no. 14. 2007.

- [22] Boris GEYNET, "Development and study of bipolar transistors with Si/SiGe :C heterojunctions for millimetric BiCMOS technology" Thesis, University of Science and Technology of Lille, Page 18, 2010 : <a href="http://doc.univ-lille1.fr">http://doc.univ-lille1.fr</a>

- [23] Boris GEYNET, "Development and study of bipolar transistors with Si/SiGe:C heterojunctions for millimetric BiCMOS technology" Thesis, University of Science and Technology of Lille, Page 22, 2010: http://doc.univ-lille1.fr

- [24] Boris GEYNET, "Development and study of bipolar transistors with Si/SiGe:C heterojunctions for millimetric BiCMOS technology" Thesis, University of Science and Technology of Lille, Page 23, 2010: http://doc.univ-lille1.fr

- [25] Miller SL, "Ionization rates for electrons and holes in silicon", Phys. Rev. 99, 1955, Page(s): 1234

- [26] Rickelt, M., Rein, HM., Rose, E., "Influence of impact-ionization-induced instabilities on the maximum usable output voltage of Si-bipolar transistors", IEEE Transactions on Electron Devices, Volume 48, April 2001, Page (s): 777-783

- [27] Martinuzzi. S, Crystalline silicon solar cells, Reflets de la physics, Dossier Photovoltaique, Dec. 2007, page(s) 11-13